3-2 Key characteristics for protection against ESD events(2)

3-2(2) Low clamp voltage (VC) and first peak voltage

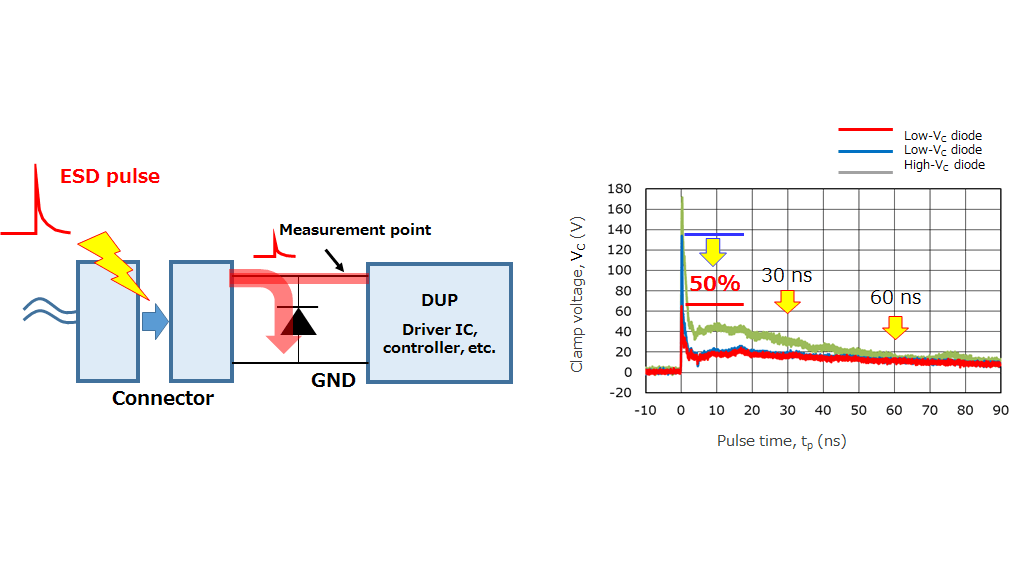

Figure 3.10 shows the response waveforms of ESD protection diodes with high and low clamp voltages (VC) when an ESD waveform stipulated in IEC 61000-4-2 was applied to them. These waveforms were taken at the input of a device under protection (DUP). The ESD protection diode with a lower VC exhibits lower clamp voltage at 30 ns and 60 ns than the one with a higher VC. The smaller the area under the curve of the ESD waveform, the less damage the DUP suffers. Therefore, ESD protection diodes with low VC provide better protection against ESD pulses. In addition, some ESD protection diodes do not respond immediately after the ESD entry. Therefore, if the first peak of the ESD pulse is higher than the VC of the ESD protection diode, it might be applied to the DUP, leading to its malfunction or destruction. ESD protection diodes are designed to provide faster response than other types of protection devices. In addition, Toshiba is working on the optimization of the chip process and the internal device structure in order to further reduce the first peak voltage and therefore provide more rugged protection against the peak ESD voltage during the initial period.

3 Key electrical characteristics of TVS diodes (ESD protection diodes)

- 1 What is a TVS diode (ESD protection diode)?

- 2 Basic operations of TVS diodes (ESD protection diodes)

- 4 Selection guidelines for TVS diodes (ESD protection diodes)

- 5 Layout considerations for TVS diodes (ESD protection diodes)

- 6 Absolute maximum ratings of TVS diodes (ESD protection diodes)

- 7 Electrical characteristics of TVS diodes (ESD protection diodes)

Related information

- Product Web Page

TVS Diodes (ESD protection diodes) - Applidcation Notes

Diode - FAQ

TVS diodes (ESD protection diodes) - Parametric searches for all Toshiba TVS diode (ESD protection diodes) produ cts are available here:

Parametric search - Stock Check & Purchase Toshiba TVS diode (ESD protection diodes) here

Stock Check & Purchase